ARM instruction set has not changed very much at all since then and is in many chips in nearly every device. More are made than any other design.

She is also trans and transitioned in 1990s. Being a cis woman in technology can be frustrating even today. She was a trans woman in UK tech in 1990s.

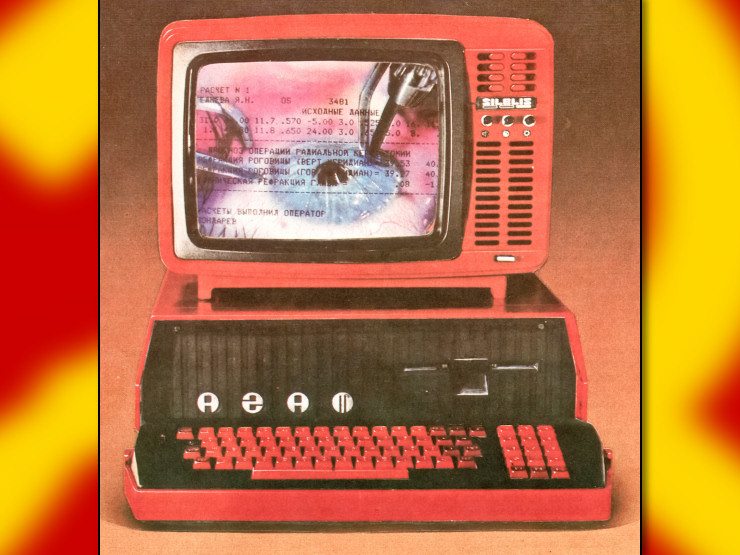

This is a innovator in technology. Not Jobs, not Musk, not Gates. Wilson created the CPU design which is cheap, simple, efficient, strong, and has become universal today.

CISC architecture BTFO.

All new modern CISC designs are actually trans(decoded) RISC designs. This is what the feminists want to do to men.

:hahaha:

godspeed, feminists

deleted by creator

True, it's more complicated than that, everything is. But I wanted to make a CISC/cis pun.

deleted by creator

The insidious LGBT agenda! :HEYAYA:

This is mostly true for the powerful systems like computers and mobiles, but x86 is not a feasible architecture for very weak embedded system. This is my area of work, and there are significant differences which still matter between RISC and CISC in this space because we do not have the option to simply throw more resources at problems. There are applications for both, but Thumb makes ARM hard to beat and the number of conditional instructions is very helpful for tight code. It is a very suitable instruction set to small, simple processors.

I do not agree that the memory model are on par however, but I really hate the x86 memory model and I think it has too many crutches that lead to bad code which is only discovered when attempting to port.

deleted by creator

deleted by creator

It does this using micro operations which essentially make it a RISC-ish processor with a CISC interface. All of the CISC features are baggage. We do not like instructions which operate on memory especially, as memory is not synchronized with the processor since 6502 days.

True CISC designs can be tightly pipelined, but there are severe limitations, and such designs were abandoned in 1990s.

deleted by creator

i thought it was a pun